Company News

Aug. 22, 2024

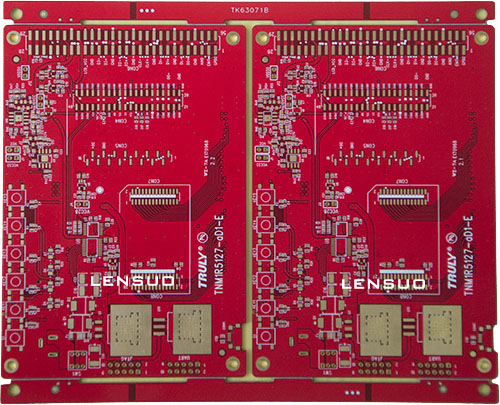

Multilayer PCB laminate structure produced by PCB Manufacturer

Before designing a multilayer printed circuit board, the designer must determine the board structure (CEM) based on the size of the circuit, the size of the printed circuit board, and the electromagnetic compatibility requirements, that is, using four, six, or more boards.

The cascade structure is an important factor affecting the CEM performance of the printed circuit board, and is also an important means for suppressing electromagnetic interference. This section describes the relevant content of polychlorinated biphenyl multilayer laminate structures.

1.1 Layer and Overlay Selection Principles There are many factors that must be considered when determining the laminate structure of a polychlorinated biphenyl multilayer.

In terms of wiring, more layers are high, and the best is wiring, but the cost and difficulty of the card will increase.

For manufacturers, the symmetry of the stacked structure is extensively analyzed during the manufacturing process of the printed circuit board. Therefore, the selection of each layer must take into account all aspects required in order to achieve maximum balance.

For experienced designers, after the component is preset, the printed circuit routing bottleneck will be analyzed, combined with other EDA tools, to analyze the cable density of the printed circuit, followed by the number and type of signal lines with special wiring requirements.

1.2 Common Cascading Structure The following is an example of a 4-Layer PCB produced by PCB Supplier that illustrates how to optimize the arrangement and combination of different cascading structures. There are several different stacking modes (up and down) on the four-layer fluent four-layer board.

So how do we choose between the first plan and the second plan? In general, the designer will choose Figure 1 as the structure of the four-layer board.

However, the common printed circuit board only places the components on the upper layer. Therefore, it is best to use Frame 1. However, when the upper and lower layers must place the thickness between the component and the internal power layer and the layer between the larger layers, and the coupling is not good, it is necessary to consider the layer of at least one signal line.

There are fewer signal lines in the lower layer and a large copper surface can be used for coupling the power layer.

Instead, if the part is primarily on the lower level, the map is implemented. The power layer and the yarn layer are themselves coupled.

In view of the symmetry requirements, Outline 1 is generally accepted.

Previous: How Can PCBA Suppliers Stand Out From The Competition?

Next: Company